半導体の微細化という「土台」

半導体の微細化は、1世代ごとに70%の割合で進められる。そして、70%の微細化を行うと、さまざまな問題が、まるでパンドラの箱を開けたように噴出する。

微細化を進めるときの課題は、トランジスタの構造だけではないのである。これらの問題を論じる前に、多分に感覚的ではあるが、半導体の微細化を進めるとはどういうことかを述べたい。あらゆる問題を一つ一つ解決していかなければ、新しい世代の半導体は量産できないのである。

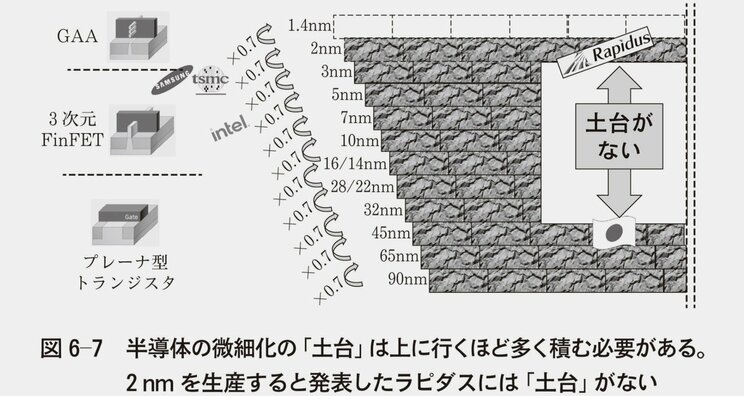

半導体の微細化を進めるということは、ピラミッドを構築することに似ているかもしれない。ピラミッドの上に行けば行くほど、石を積むことが難しくなるからだ。しかし違いもある。それは、半導体の微細化が進むほど、積み上げなければならないものが多くなるため、半導体の微細化というピラミッドは逆三角形型になるという点だ(図6─7)。

その逆ピラミッド型の「土台」において、2022年12月末時点で、TSMCが3nmに到達し、サムスンは3nmの歩留りが上がらず5/4nmに留まっており、インテルが10nm~7nmから先に進めずにいる。そして、日本は40nmレベルで停滞したままだ。

このように、逆ピラミッド型の「土台」を形成しながら進める半導体の微細化において、ある微細化の世代をスキップするということは、あり得ない。というのは、ある技術世代の「土台」なしには次の世代に進むことができないからだ。

ラピダスには微細化の「土台」がない

ラピダスには、米IBMと、欧州のコンソーシアムimecが技術提携することになった。しかし、40nmレベルから3nmまでの技術の蓄積が全くないラピダスに、誰が何を協力しても、2nmの量産はできないだろう。

その理由を一言でいうと、ラピダスには微細化の「土台」が全くないからだ。「土台」を一つずつ積んできたTSMC、サムスン、インテルですら、さらに微細化を進めることに、大変な努力を強いられている。

にもかかわらず、何の微細化の「土台」も持っていないラピダスが、9世代も微細化をスキップして、いきなり2nmのロジック半導体を量産することはできるはずがない。これは、火を見るより明らかなことである。

筆者から一つ提案がある。いきなり2nmはいくらなんでも無理だから、2023年前半に32nm、後半に28/22nm、2024年前半にFinFETの16/14nm、後半に10nm、2025年前半に7nm、後半に5nm、2026年前半に3nm、後半にGAA構造の2nmと、開発を試作でいいから、一歩一歩、着実に「土台」を積み上げていったらどうだろうか。

その方が確実であるし、計画通りに進めば、もしかしたら、「2027年に2nm」を量産できるかもしれない。

「急がば回れ」ともいうし、「急いては事を仕損ずる」ともいう。ラピダス関係者は、今一度、計画を考え直すべきである。

以上、半導体の微細化を進めるとはどういうことかという概念を説明した。以下では、ラピダスが米IBMや欧州imecの協力を得ながらも、2nmのロジック半導体を量産するために、具体的にどのような問題があるかを論じる。